## Reconfigurable, High Density, High Speed, Low Power, Radiation Hardened FPGA Technology MAPLD2008

S.Ramaswamy<sup>1</sup>, Leonard Rockett<sup>1</sup>,, Dinu Patel<sup>1</sup>, Steven Danziger<sup>1</sup> Rajit Manohar<sup>2</sup>, Clinton W. Kelly, IV<sup>2</sup>, John Lofton Holt<sup>2</sup>, V. Ekanayake<sup>2</sup>, Dan Elftmann<sup>2</sup> Ken LaBel, Melanie Berg etc. NASA<sup>3</sup>

<sup>1</sup>BAE SYSTEMS, 9300 Wellington Road, Manassas, VA, 20110, USA

<sup>2</sup>Achronix Semiconductor Corporation, 333 W. San Carlos Street, San Jose, CA, 95110, USA <sup>3</sup>NASA Goddard

- RHFPGA Roadmap

- RHFPGA Product Features

- Achronix Technology Overview

- BAE Radiation Hardened Process Technology Overview

- Program Status / Summary

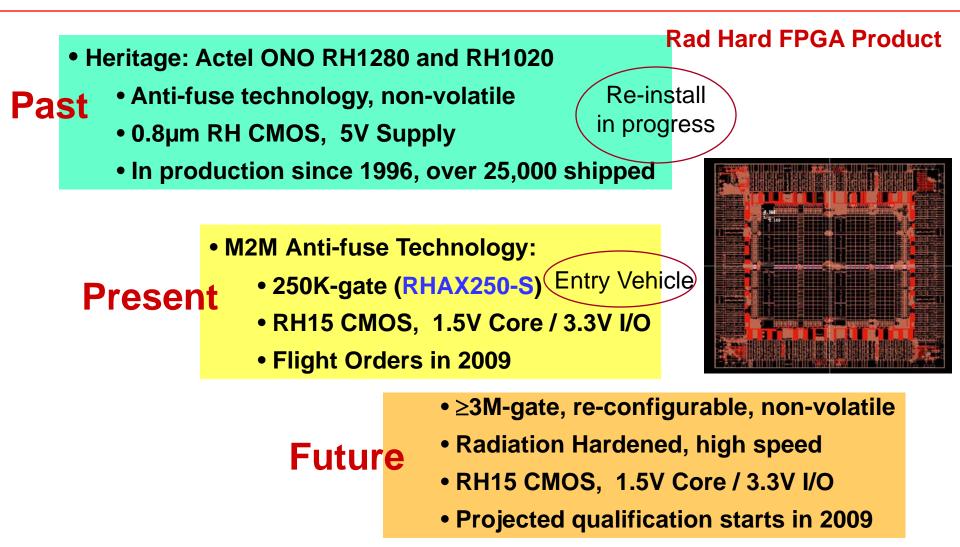

### **Radiation Hardened FPGA Roadmap**

# **RHFPGA Product Features**

- TID tolerance of > 1Mrad Si

- SEU immunity < 10<sup>-11</sup>errors/bit-day

- System speeds > 300MHz

- Support of RADHARD IOs and RAMs for integration into Systems

- Reconfigurable/Reprogrammable

- Low Power

- Extreme Temperature Operation

- Non Volatile

- EMP Protected

- Full Compatibility with Existing EDA Tools

- Product Name -> Radrunner

# **Achronix Company Overview**

- Privately held fabless semiconductor company founded in New York in 2004

- Achronix has received \$34.4M Series A funding

- Founders developed technology in 1998 at Cornell University

- Headquartered in San Jose, CA

- Working 90 and 180 nm prototype silicon

- Partnerships with the world leading foundry TSMC, BAE Systems and numerous IP & EDA vendors

- 65 nm commercial FPGA silicon has been received from TSMC; currently shipping

- All Key IP's protected by patents

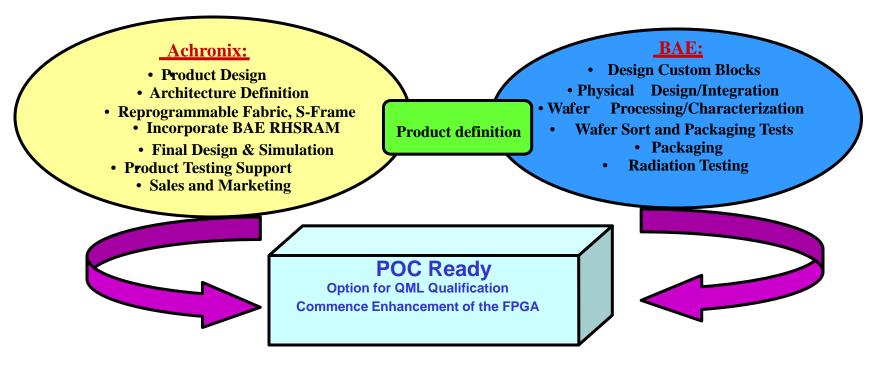

### **BAE SYSTEMS** Reconfigurable RHFPGA Proof of Concept

### **Key Roles to support Reconfigurable RHFPGA Proof of Concept:**

#### ACX RHFPGA Product Development.... A collaborative effort

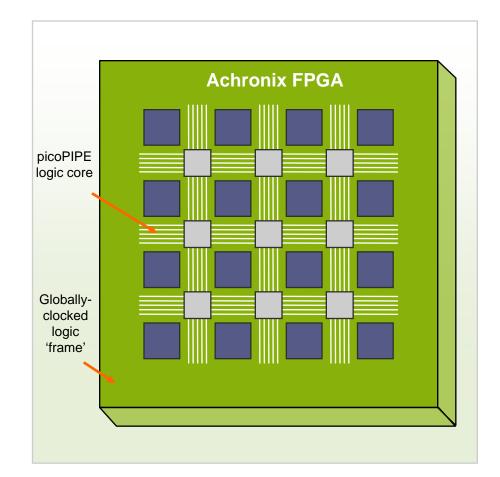

# Achronix RHFPGA Technology

## **Achronix Core Technology**

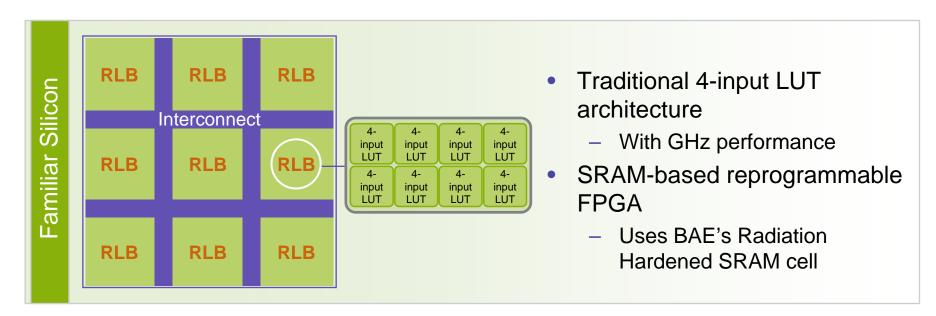

- Core contains 'picoPIPE' technology used for both logic and routing

- You do not need to know the details in order to benefit from this

- Fully synchronous I/O 'frame' surrounds the core

- picoPIPE technology is used to implement synchronous hardware

- A design is input using a HDL such as RTL

- The RTL does not need to be targeted to picoPIPE technology

### Looks like a regular FPGA, but has approx 4x throughput

## **Data Tokens**

#### **BAE SYSTEMS**

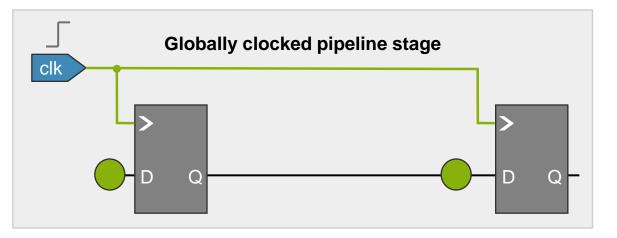

#### **Traditional FPGA**

- In globally-clocked logic, a data value at a clock edge can be considered as a "Data Token"

- Only valid data (data at a clock edge) is propagated

- Hence each register output's a new Data Token (value) at every clock edge

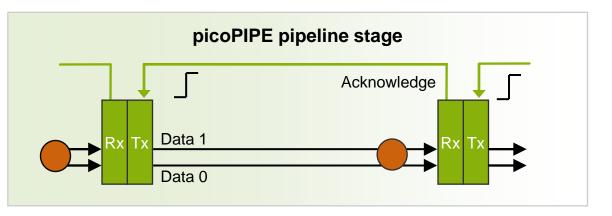

#### Achronix FPGA

- picoPIPE logic also contains Data Tokens

- Each data token uses 2 signals instead of 1

- Data validation (clock-like functionality) is performed using acknowledge instead of a global clock

## **More on Throughput**

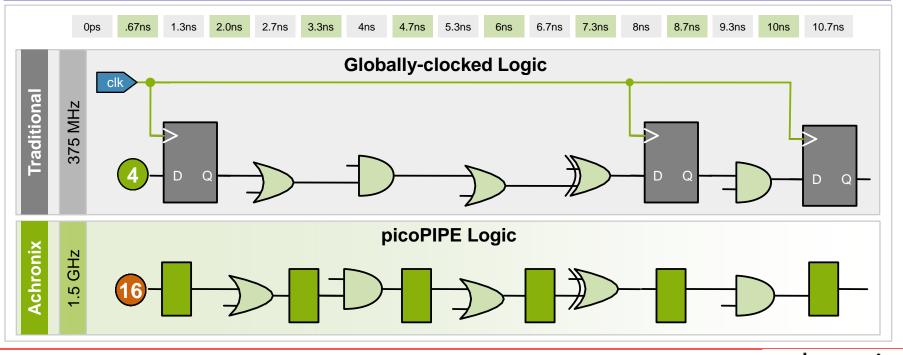

#### **Traditional FPGA**

- Globally Clocked Logic is not balanced

- The clock rate must allow for the slowest path in the entire clock domain

- Any combinatorial logic faster than the slowest path (by definition, all remaining logic) waits for the slowest one to finish

#### **Achronix FPGA**

- Achronix technology allows fine-grained pipelining

- Allows data rate to be much faster

- Pipelining also allows more data values in flight

- Equates to faster throughput

achr onix SEMICONDUCTOR CORPORATION

# Familiar Silicon & Familiar Tools

| Open Project. | Supplify Pro*                                 |              | Eithar<br>Project Project Files<br>Dasign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Activotex - Utita1 : ACXUI1206 : 10<br>Design Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|-----------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| institution   | n and Se Place and Route VHDL Netlat Reductor | Synplicity , | Control Contro | A. Region Settings  Desp Foregong/Intel  Case of Propagation prime  Grant Propagation prime Settings Market Setting Market Settings Market Settings Market Setting Ma |

| N X           | OK Great Hep                                  | 542,7        | AC2041218                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | OK Cancal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

- Synplify-Pro and Mentor Precision Synthesis Flows

- Full compatibility with existing third party simulation, debug, and verification tools

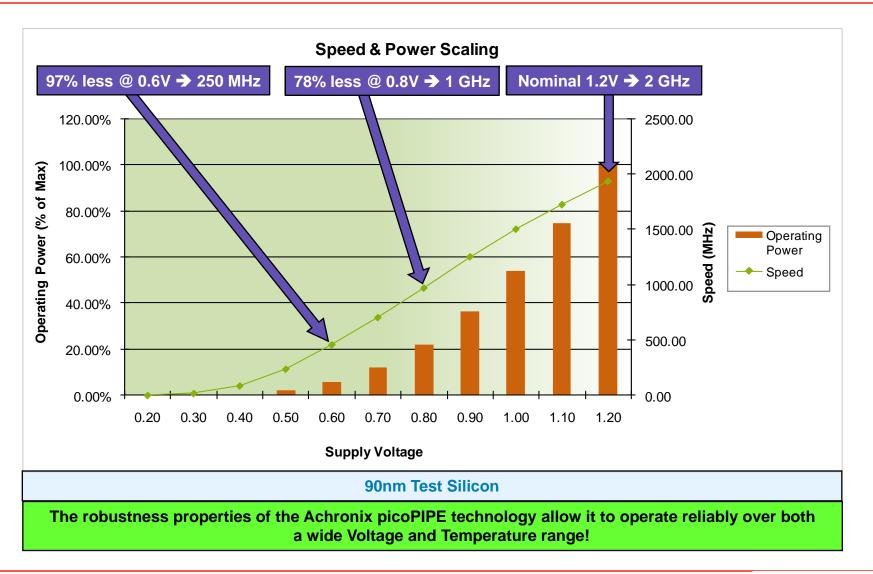

### Trading off Speed for Power Dissipation: V<sup>2</sup>f

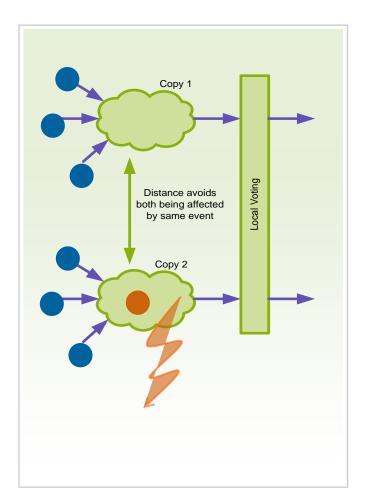

### Achronix Patented SEE Mitigation Methodology: Redundancy Voting Circuits (RVC)

- Redundancy Voting Circuits (RVC)

- Two copies of all circuits are implemented

- Copies are non-adjacent to avoid the risk of a single upset affecting both

- Every stage (combinatorial and state) has local voting mechanism

- Local voting waits until both copies agree

- no SEE, values will agree at the voter, tokens propagate

- When SEE occurs values won't agree at voter, local voter <u>blocks</u> token propagation

- After event energy dissipates the upset circuit value is resolved to the correct value and tokens propagate

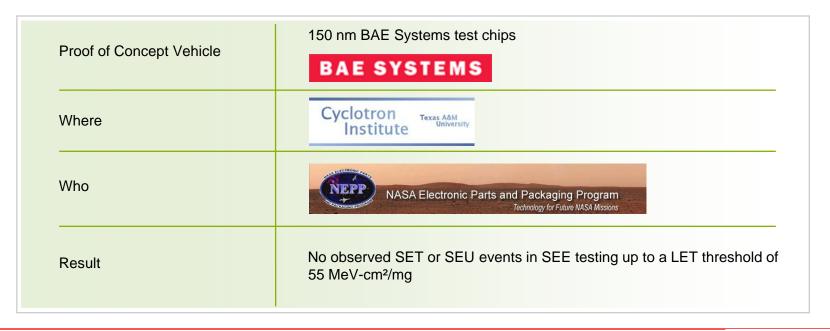

### **RVC Proof of Concept Test Chip**

- Radiation Hardened By Design (RHBD) circuit techniques portable to any foundry to enable **extremely** low SEU and SET rates (< 10<sup>-11</sup> upsets/bit day)

- Circuit technique proven thru SEE testing at 150 nm applicable to any process node

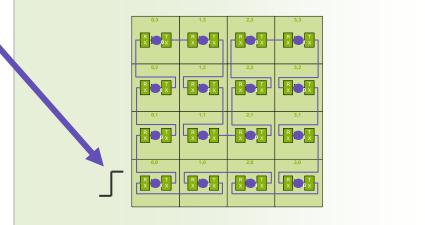

## **Rad-Hard FPGA Test Chip & Patterns**

- Defined goal of initial radiation test was to prove that tokens continue to propagate in the event of heavy ion impact

- Test Chip contained a 4x4 array of FPGA Tiles implemented with RVC picoPIPE elements

- One dedicated tile had an 8 bit counter (implemented in RVC) on output acknowledge to observe the functioning of the various FPGA configurations at a reasonable frequency with standard I/O

- Five different <u>FPGA patterns</u> utilized during testing

### Summary: Heavy Ion SEE Test of BAE-Achronix Rad-Hard FPGA Test Chip

- Testing completed by NASA at Texas A&M University Cyclotron Single Event Effects Test Facility (SEETF)

- Test Date: August 14th, 2007

- Sample size: Three devices tested including one control not exposed to the radiation source

- Flux:  $1 \times 10^3$  to  $1 \times 10^4$  particles/cm<sup>2</sup>/s

- Fluence: 5x10<sup>6</sup> particles/cm<sup>2</sup>

- **Test Angles:** Normal, 45 degree

- SEL Analysis

- No SEL observed through tests with temperatures up to 74 °C and LET of 55 MeV\*cm<sup>2</sup>/mg

- SEE Data and Analysis

- No SEFI observed for all tests run

- Tokens continued to propagate throughout testing

## **BAE RHFPGA Process Technology**

## **RHFPGA Technology (RH15F) Features**

| Key Features             |                       |

|--------------------------|-----------------------|

| Features:                | RH15                  |

| Isolation                | STI                   |

| Thin Oxide / DGO Devices | 26 Å / 70 Å           |

| Vdd Options              | 1.5 V / 1.8 V / 3.3 V |

| Metal Levels             | 7                     |

| Capacitors               | Yes                   |

| Resistors                | Yes                   |

| C4 / Wirebond            | Y/Y                   |

| Radiation Hardness Assurance Levels |       |  |  |  |

|-------------------------------------|-------|--|--|--|

| Environment                         |       |  |  |  |

| Total Dose (rad(Si))                | 1M    |  |  |  |

| SEU (errors/bit-day)                | 1E-11 |  |  |  |

| SEL (MeV-cm2/mg)                    | 120   |  |  |  |

| Neutron Fluence (n/cm2)             | 1E13  |  |  |  |

| Prompt Dose Upset (rad(Si)/s)       | 1E9   |  |  |  |

| Prompt Dose Survival (rad(Si)/s)    | 1E12  |  |  |  |

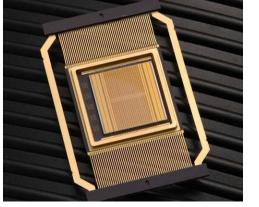

### **RH15F Process Maturity - Memory**

### 16M SRAM – Next-Generation Strategic RH SRAM

|               | -           |            |               |

|---------------|-------------|------------|---------------|

|               |             | Total ILCs | 1,063,783,005 |

| Transistors   | 113,070,511 | CA         | 298,967,451   |

| HVT NFETS     | 74,422,289  | СТ         | 226,146,395   |

| HVT PFETS     | 38,645,756  | V1         | 212,067,749   |

| DGO NFETS     | 1,630       | V2         | 242,233,858   |

| DGO PFETS     | 836         | V3         | 82,209,612    |

| R2 Resistors  | 36,410,528  | V4         | 1,011,258     |

| Q2 Capacitors | 18,205,264  | V5         | 506,746       |

|               |             | V6         | 639,936       |

| Access Time        | 15-20 ns                                                                                                                           |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Process Technology | 0.15 µm CMOS                                                                                                                       |

| Die Size           | 16 mm by 16 mm                                                                                                                     |

| Power Supply       | 1.5 V + / - 10% core<br>2.5 or 3.3 V + / - 10% I/O                                                                                 |

| Power Dissipation  | 10 mW/MHz at 1.5V (per die)<br>100 mW standby                                                                                      |

| Temperature Range  | -55°C to +125°C                                                                                                                    |

| Packaging          | 23.2 mm by 26.2 mm by 6.0 mm<br>100 pin Flat Pack (5-high stack)                                                                   |

| Radiation Hardness | Total Ionizing Dose > 1Mrad(Si)<br>Prompt Dose > 1E9 rad(Si)/sec<br>SEU < 1E-12 errors / bit-day (W.C. 90% GEO)<br>Latchup: Immune |

| ESD                | TBD                                                                                                                                |

| Screening level    | Prototype and Flight flows                                                                                                         |

| Organization       | 2Mx8 die – single chip package<br>2Mx32 4-high package<br>2Mx40 5-high package                                                     |

512Kx32 die - single chip package

#### **Configuration Memory Cell for RHFPGA uses the 16M SRAM Cell**

achronix SEMICONDUCTOR CORPORATION

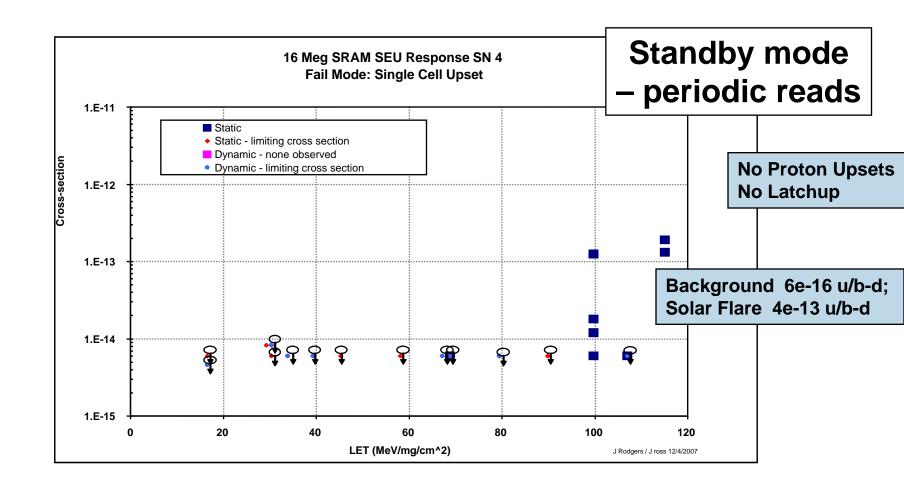

### 16M SRAM Heavy Ion Test Results Memory Cell Upset

SEU for Memory Cell Exceeds RHFPGA SEU Targets

### **RH15F Qualification Vehicle (16MSRAM)**

| BA | E S | YSI | ΕN | 1S |

|----|-----|-----|----|----|

|    |     |     |    |    |

| Parameter                                                        | Requirement              | Goal                 | Achieved      | Outlook |

|------------------------------------------------------------------|--------------------------|----------------------|---------------|---------|

| Operating Speed - worst case<br>125C and post radiation          | ≤ 20 ns                  | ≤ 15 ns              | ≤ 15 ns       | G       |

| Operating Temperature Range<br>Full Performance<br>Functionality | 0 to 80C<br>-55C to 125C | -55C to 125C<br>Same | -55C to 125C  | G       |

| Standby Current - worst case<br>125C and post radiation          | ≤ 60 mA                  | ≤ 40 mA              | ≤ 40 mA       | G       |

| SEU (upsets/bit-day)                                             | < 1E-10                  | < 1E-11              | << 1E-12      | G       |

| Total Ionizing Dose - Gamma                                      | ≥ 0.5 Mrad               | ≥ 1Mrad              | ≥ 1Mrad       | G       |

| Prompt Dose Upset (rad/sec)                                      | ≥ 1E9                    | ≥ 1E9                | Planned on    | G       |

| Survivability (rad/sec)                                          | 1E12                     | 1E12                 | 5-high stacks | G       |

Characterization complete

**Qualification in progress, Prototypes Samples Available**

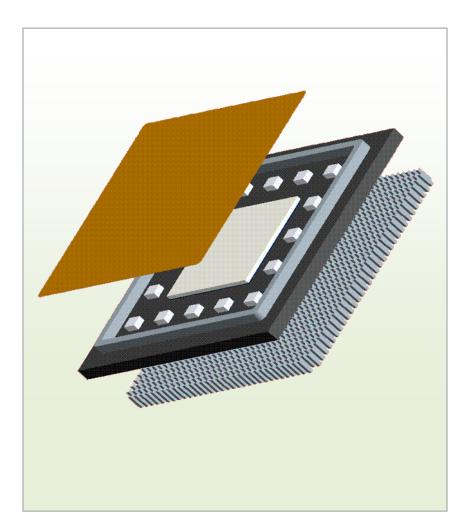

# **RHFPGA Package Definition**

- Substrate- ceramic 32 mm x 32 mm

- 32 mm x 32 mm Column Grid Array

- 1.27 mm pitch

- 624 Total I/O

- Capacitors

- -Sizing suggests 16 Low Inductance Flip Chip Capacitor Sites

- -Can be used to support several different voltages

- Hermetic Seam Weld Sealing

|                     | Radrunner Family (150 nm)   |        |         |  |  |

|---------------------|-----------------------------|--------|---------|--|--|

|                     | Device Name                 | RDR500 | RDR1000 |  |  |

|                     | LUT                         | 4,320  | 8,640   |  |  |

| S                   | Number of 18 Kbit Block RAM | 5      | 10      |  |  |

| Device<br>Resources | Block RAM (Kbit)            | 90     | 180     |  |  |

|                     | Number of PLL               | 4      | 4       |  |  |

|                     | SpaceWire Interfaces        | 4      | 7       |  |  |

|                     | User Programmable I/O       | 336    | 384     |  |  |

| age                 | CCGA624 (32 mm x 32 mm)     |        | 384     |  |  |

| Package             | CQ340                       | 286    |         |  |  |

#### Design under optimization to maximize RHFPGA Resources

# SUMMARY

- Program Fulfills Critical Need for Reconfigurable RH FPGAs for Strategic Applications

- Excellent Partnership between BAE Systems and Achronix Ongoing

- Initial Achronix Commercial Chip First Pass Success

- Test Chip Functionality Demonstrated, Radiation Testing Successful

- Design Activities Continuing with No Technical Concerns

- Plans In Place for Further Device Enhancements

### **Program Outlook Overall Positive for Initial POC Device 2Q09**